Counters problems

- 1. A 22-MHz clock signal is put into a MOD-16 counter. What is the frequency of the Q output of each stage of the counter?

Options- A. Q1 = 22 MHz, Q2 = 11 MHz, Q3 = 5.5 MHz, Q4 = 2.75 MHz

- B. Q1 = 11 MHz, Q2 = 5.5 MHz, Q3 = 2.75 MHz, Q4 = 1.375 MHz

- C. Q1 = 11 MHz, Q2 = 11 MHz, Q3 = 11 MHz, Q4 = 11 MHz

- D. Q1 = 22 MHz, Q2 = 22 MHz, Q3 = 22 MHz, Q4 = 22 MHz Discuss

Correct Answer: Q1 = 11 MHz, Q2 = 5.5 MHz, Q3 = 2.75 MHz, Q4 = 1.375 MHz

- 2. The final output of a modulus-8 counter occurs one time for every ________.

Options- A. 8 clock pulses

- B. 16 clock pulses

- C. 24 clock pulses

- D. 32 clock pulses Discuss

Correct Answer: 8 clock pulses

- 3. How many AND gates would be required to completely decode ALL the states of a MOD-64 counter, and how many inputs must each AND gate have?

Options- A. 128 gates, 6 inputs to each gate

- B. 64 gates, 5 inputs to each gate

- C. 64 gates, 6 inputs to each gate

- D. 128 gates, 5 inputs to each gate Discuss

Correct Answer: 64 gates, 6 inputs to each gate

- 4. A 4-bit counter has a maximum modulus of ________.

Options- A. 3

- B. 6

- C. 8

- D. 16 Discuss

Correct Answer: 16

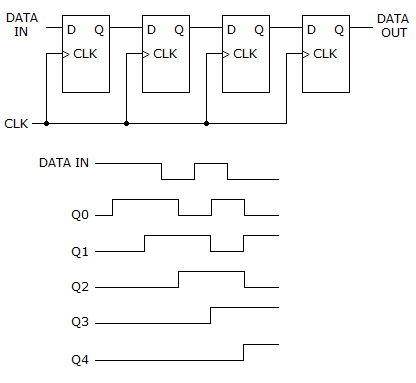

- 5. How many data bits can be stored in the register shown below?

Options- A. 5

- B. 32

- C. 31

- D. 4 Discuss

Correct Answer: 5

- 6. A seven-segment, common-anode LED display is designed for:

Options- A. all cathodes to be wired together

- B. one common LED

- C. a HIGH to turn off each segment

- D. disorientation of segment modules Discuss

Correct Answer: a HIGH to turn off each segment

- 7. An asynchronous 4-bit binary down counter changes from count 2 to count 3. How many transitional states are required?

Options- A. None

- B. One

- C. Two

- D. Fifteen Discuss

Correct Answer: Fifteen

- 8. Synchronous counters eliminate the delay problems encountered with asynchronous counters because the:

Options- A. input clock pulses are applied only to the first and last stages

- B. input clock pulses are applied only to the last stage

- C. input clock pulses are not used to activate any of the counter stages

- D. input clock pulses are applied simultaneously to each stage Discuss

Correct Answer: input clock pulses are applied simultaneously to each stage

- 9. In an HDL ring counter, many invalid states are included in the programming by:

Options- A. using a case statement.

- B. using an elsif statement.

- C. including them under others.

- D. the ser_in line. Discuss

Correct Answer: including them under others.

- 10. List which pins need to be connected together on a 7493 to make a MOD-12 counter.

Options- A. 12 to 1, 11 to 3, 9 to 2

- B. 12 to 1, 11 to 3, 12 to 2

- C. 12 to 1, 11 to 3, 8 to 2

- D. 12 to 1, 11 to 3, 1 to 2 Discuss

Correct Answer: 12 to 1, 11 to 3, 8 to 2

More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.