Combinational Logic Circuits problems

- 1. What is the indication of a short on the input of a load gate?

Options- A. Only the output of the defective gate is affected.

- B. There is a signal loss to all gates on the node.

- C. The affected node will be stuck in the LOW state.

- D. There is a signal loss to all gates on the node, and the affected node will be stuck in the LOW state. Discuss

Correct Answer: There is a signal loss to all gates on the node, and the affected node will be stuck in the LOW state.

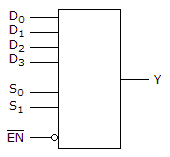

- 2. For the device shown here, assume the D input is LOW, both S inputs are LOW, and the

input is LOW. What is the status of the

input is LOW. What is the status of the  outputs?

outputs?

Options- A. All are HIGH.

- B. All are LOW.

- C. All but

are LOW.

are LOW. - D. All but

are HIGH.

Discuss

are HIGH.

Discuss

Correct Answer: All but

are HIGH.

are HIGH. - 3. A logic probe is placed on the output of a gate and the display indicator is dim. A pulser is used on each of the input terminals, but the output indication does not change. What is wrong?

Options- A. The output of the gate appears to be open.

- B. The dim indication on the logic probe indicates that the supply voltage is probably low.

- C. The dim indication is a result of a bad ground connection on the logic probe.

- D. The gate may be a tristate device. Discuss

Correct Answer: The output of the gate appears to be open.

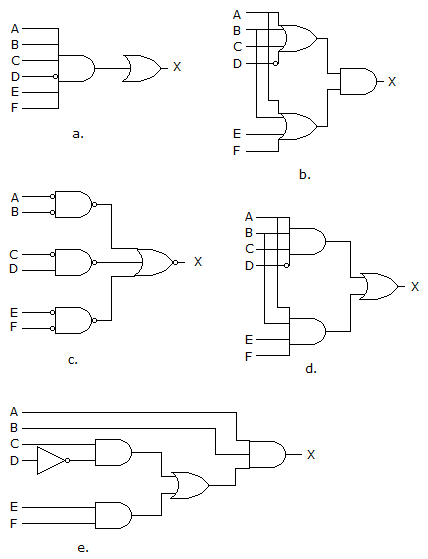

- 4. Which of the circuits in figure (a to d) is the sum-of-products implementation of figure (e)?

Options- A. a

- B. b

- C. c

- D. d Discuss

Correct Answer: d

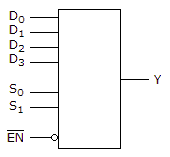

- 5. For the device shown here, let all D inputs be LOW, both S inputs be HIGH, and the

input be LOW. What is the status of the Y output?

input be LOW. What is the status of the Y output?

Options- A. LOW

- B. HIGH

- C. Don't Care

- D. Cannot be determined Discuss

Correct Answer: LOW

- 6. For the device shown here, let all D inputs be LOW, both S inputs be HIGH, and the

input be HIGH. What is the status of the Y output?

input be HIGH. What is the status of the Y output?

Options- A. LOW

- B. HIGH

- C. Don't Care

- D. Cannot be determined Discuss

Correct Answer: LOW

- 7. How many 1-of-16 decoders are required for decoding a 7-bit binary number?

Options- A. 5

- B. 6

- C. 7

- D. 8 Also asked in: Bank Exams

Correct Answer: 8

- 8. What is the indication of a short to ground in the output of a driving gate?

Options- A. Only the output of the defective gate is affected.

- B. There is a signal loss to all load gates.

- C. The node may be stuck in either the HIGH or the LOW state.

- D. The affected node will be stuck in the HIGH state. Discuss

Correct Answer: There is a signal loss to all load gates.

- 9. When adding an even parity bit to the code 110010, the result is ________.

Options- A. 1110010

- B. 1111001

- C. 110010

- D. 001101 Discuss

Correct Answer: 1110010

- 10. The design concept of using building blocks of circuits in a PLD program is called a(n):

Options- A. hierarchical design.

- B. architectural design.

- C. digital design.

- D. verilog. Discuss

Correct Answer: hierarchical design.

More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.