Discussion

Home ‣ Digital Electronics ‣ Programmable Logic Device See What Others Are Saying!

- Question

Which is a mode of operation of the GAL16V8?

Options- A. Simple mode

- B. Complex mode

- C. Registered mode

- D. All of the above

- Correct Answer

- All of the above

- 1. A current-sourcing transistor may also be referred to as a pull-down transistor.

Options- A. True

- B. False Discuss

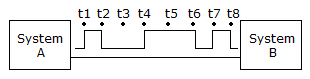

- 2. The value of the data shown in the given figure is ________.

Options- A. between 0 and 1

- B. 1011001

- C. 5

- D. 1001101 Discuss

- 3. How many combinations are handled in an LUT?

Options- A. 4

- B. 8

- C. 16

- D. 32 Discuss

- 4. As a rule, CMOS has the lowest power consumption of all IC families.

Options- A. True

- B. False Discuss

- 5. In a FLEX10K device, the carry chain provides a fast carry forward function between ________.

Options- A. LUTs

- B. EABs

- C. LEs

- D. LABs Discuss

- 6. When two counters are cascaded, the overall MOD number is equal to the ________ of their individual MOD numbers.

Options- A. product

- B. sum

- C. log

- D. reciprocal Discuss

- 7. A parallel load operation is asynchronous, so it is not dependent on the clock.

Options- A. True

- B. False Discuss

- 8. The 2's complement of the binary number 1000 is ________.

Options- A. 111

- B. 0110

- C. 1110

- D. 1000 Discuss

- 9. It is normal for more than one decoder output to be active at the same time.

Options- A. True

- B. False Discuss

- 10. How many outputs would two 8-line-to-3-line encoders, expanded to a 16-line-to-4-line encoder, have?

Options- A. 3

- B. 4

- C. 5

- D. 6 Discuss

More questions

Correct Answer: False

Correct Answer: 1011001

Correct Answer: 16

Correct Answer: True

Correct Answer: LEs

Correct Answer: product

Correct Answer: True

Correct Answer: 1000

Correct Answer: False

Correct Answer: 4

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.