Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Circuits Comments

- Question

How many outputs would two 8-line-to-3-line encoders, expanded to a 16-line-to-4-line encoder, have?

Options- A. 3

- B. 4

- C. 5

- D. 6

- Correct Answer

- 4

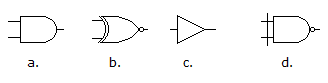

- 1. Which of the figures shown below represents the exclusive-NOR gate?

Options- A. a

- B. b

- C. c

- D. d Discuss

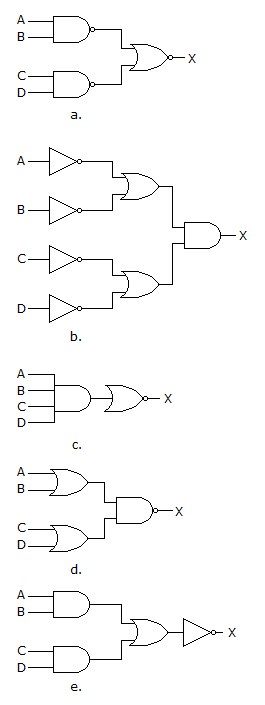

- 2. Which of the figures in figure (a to d) is equivalent to figure (e)?

Options- A. a

- B. b

- C. c

- D. d Discuss

- 3. Which of the following combinations cannot be combined into K-map groups?

Options- A. Corners in the same row

- B. Corners in the same column

- C. Diagonal corners

- D. Overlapping combinations Discuss

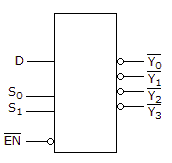

- 4. The device shown here is most likely a ________.

Options- A. comparator

- B. multiplexer

- C. demultiplexer

- D. parity generator Discuss

- 5. Two 4-bit binary numbers (1011 and 1111) are applied to a 4-bit parallel adder. The carry input is 1. What are the values for the sum and carry output?

Options- A. ∑4∑3∑2∑1 = 0111, Cout = 0

- B. ∑4∑3∑2∑1 = 1111, Cout = 1

- C. ∑4∑3∑2∑1 = 1011, Cout = 1

- D. ∑4∑3∑2∑1 = 1100, Cout = 1 Discuss

- 6. Looping on a K-map always results in the elimination of:

Options- A. variables within the loop that appear only in their complemented form.

- B. variables that remain unchanged within the loop.

- C. variables within the loop that appear in both complemented and uncomplemented form.

- D. variables within the loop that appear only in their uncomplemented form. Discuss

- 7. Which of the following is an important feature of the sum-of-products form of expressions?

Options- A. All logic circuits are reduced to nothing more than simple AND and OR operations.

- B. The delay times are greatly reduced over other forms.

- C. No signal must pass through more than two gates, not including inverters.

- D. The maximum number of gates that any signal must pass through is reduced by a factor of two. Discuss

- 8. In VHDL, macrofunctions is/are:

Options- A. digital circuits.

- B. analog circuits.

- C. a set of bit vectors.

- D. preprogrammed TTL devices. Discuss

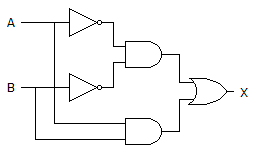

- 9. What type of logic circuit is represented by the figure shown below?

Options- A. XOR

- B. XNOR

- C. XAND

- D. XNAND Discuss

- 10. What will a design engineer do after he/she is satisfied that the design will work?

Options- A. Put it in a flow chart

- B. Program a chip and test it

- C. Give the design to a technician to verify the design

- D. Perform a vector test Discuss

Combinational Logic Circuits problems

Search Results

Correct Answer: b

Correct Answer: b

Correct Answer: Diagonal corners

Correct Answer: demultiplexer

Correct Answer: ∑4∑3∑2∑1 = 1011, Cout = 1

Correct Answer: variables within the loop that appear in both complemented and uncomplemented form.

Correct Answer: All logic circuits are reduced to nothing more than simple AND and OR operations.

Correct Answer: preprogrammed TTL devices.

Correct Answer: XNOR

Correct Answer: Program a chip and test it

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.