Discussion

Home ‣ Digital Electronics ‣ Counters Comments

- Question

A ripple counter's speed is limited by the propagation delay of:

Options- A. each flip-flop

- B. all flip-flops and gates

- C. the flip-flops only with gates

- D. only circuit gates

- Correct Answer

- each flip-flop

- 1. A MOD-12 and a MOD-10 counter are cascaded. Determine the output frequency if the input clock frequency is 60 MHz.

Options- A. 500 kHz

- B. 1,500 kHz

- C. 6 MHz

- D. 5 MHz Discuss

- 2. For a multistage counter to be truly synchronous, the ________ of each stage must be connected to ________.

Options- A. Cp, the same clock input line

- B. CE, the same clock input line

- C.

, the terminal count output

, the terminal count output - D.

, both clock input lines

Discuss

, both clock input lines

Discuss

- 3. Which segments (by letter) of a seven-segment display need to be active in order to display a digit 6?

Options- A. b, c, d, e, f, and g

- B. a, c, d, e, f, and g

- C. a, b, c, d, and f

- D. b, c, d, e, and f Discuss

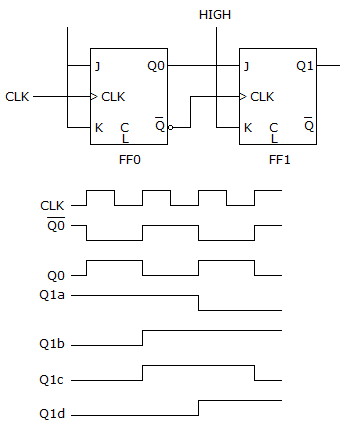

- 4. The circuit given below has no output on Q1 when examined with an oscilloscope. All J-K inputs are HIGH, the CLK signal is present, and the Q0 is toggling. The C input of FF1 is a constant LOW. What could be causing the problem?

Options- A. The Q0 output should be connected to the J input of FF1.

- B. The output of FF0 may be shorted to ground.

- C. The input of FF1 may be shorted to ground.

- D. Either the output of FF0 or the input of FF1 may be shorted to ground. Discuss

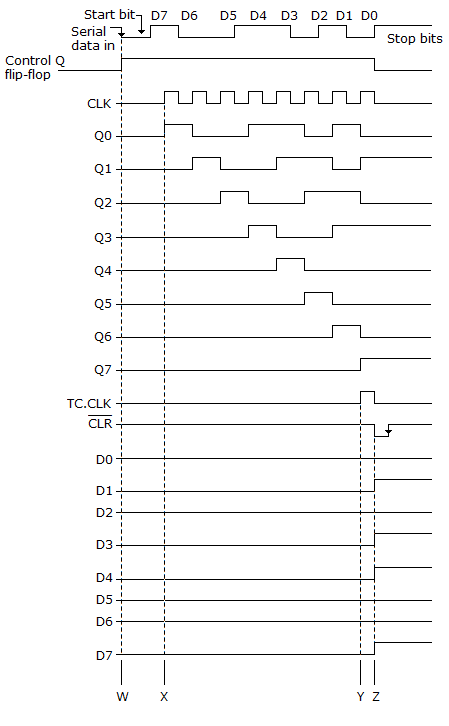

- 5. Referring to the given figure, what causes the Control FF to reset after D7?

Options- A. Once the data cycle is initiated by the Start bit, the one-shot produces an output pulse equal to the duration of the eight data bits. Once the eight data bits have been transferred to the data input register, the falling edge of the one-shot pulse resets the Control FF to start the sequence all over again.

- B. After counting the eight data bits, the divide-by-8 counter produces an output on its active-LOW CLR line to reset the Control FF.

- C. After counting eight clock pulses equivalent to eight data periods, the terminal count of the divide-by-8 counter and the clock trigger the one-shot, which in turn resets the Control FF and divide-by-8 circuits to begin the sequence all over again. Simultaneously the data is transferred through the output register.

- D. When the data output register is full, it produces an output on its C terminal that triggers the one-shot, which in turn resets the Control FF. Discuss

- 6. How is an encoder different from a decoder?

Options- A. The output of an encoder is a binary code for 1-of-N input.

- B. The output of a decoder is a binary code for 1-of-N input. Discuss

- 7. Which of the following is not a weighted value positional numbering system:

Options- A. hexadecimal

- B. binary-coded decimal

- C. binary

- D. octal Discuss

- 8. What do the mathematical symbols A < b and A > B mean?

Options- A. A < B means A is greater than B. A > B means A is less than B.

- B. A > B means A is less than B. A < B means A is greater than B.

- C. A < B means A is less than B. A > B means A is greater than B. Discuss

- 9. What is the status of the inputs S0, S1, and S2 of the 74151 eight-line multiplexer in order for the output Y to be a copy of input I5?

Options- A. S0 = 0, S1 = 1, S2 = 0

- B. S0 = 0, S1 = 0, S2 = 1

- C. S0 = 1, S1 = 1, S2 = 0

- D. S0 = 1, S1 = 0, S2 = 1 Discuss

- 10. Most demultiplexers facilitate which type of conversion?

Options- A. decimal-to-hexadecimal

- B. single input, multiple outputs

- C. ac to dc

- D. odd parity to even parity Discuss

Counters problems

Search Results

Correct Answer: 500 kHz

Correct Answer: Cp, the same clock input line

Correct Answer: a, c, d, e, f, and g

Correct Answer: Either the output of FF0 or the input of FF1 may be shorted to ground.

Correct Answer: After counting eight clock pulses equivalent to eight data periods, the terminal count of the divide-by-8 counter and the clock trigger the one-shot, which in turn resets the Control FF and divide-by-8 circuits to begin the sequence all over again. Simultaneously the data is transferred through the output register.

Correct Answer: The output of an encoder is a binary code for 1-of-N input.

Correct Answer: binary-coded decimal

Correct Answer: A < B means A is less than B. A > B means A is greater than B.

Correct Answer: S0 = 1, S1 = 0, S2 = 1

Correct Answer: single input, multiple outputs

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.