Discussion

Home ‣ Digital Electronics ‣ Counters Comments

- Question

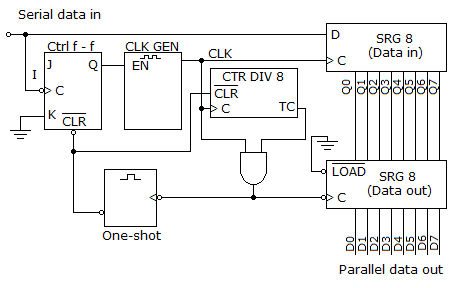

What function does the CTR DIV 8 circuit given below perform?

Options- A. It divides the clock frequency down to match the frequency of the serial data in.

- B. The divide-by-8 counter is triggered by the control flip-flop and clock, which then allows the data output register to begin storing the input data. Once all eight data bits are stored in the data output register, the data output register and the divide-by-8 counter trigger the one-shot. The one-shot then begins the process all over again.

- C. The divide-by-8 counter is used to verify that the parity bit is attached to the input data string.

- D. It keeps track of the eight data bits, triggering the transfer of the data through the output register and the one-shot, which then resets the control flip-flop and divide-by-8 counter.

- Correct Answer

- It keeps track of the eight data bits, triggering the transfer of the data through the output register and the one-shot, which then resets the control flip-flop and divide-by-8 counter.

- 1. Three cascaded modulus-5 counters have an overall modulus of ________.

Options- A. 5

- B. 25

- C. 125

- D. 500 Discuss

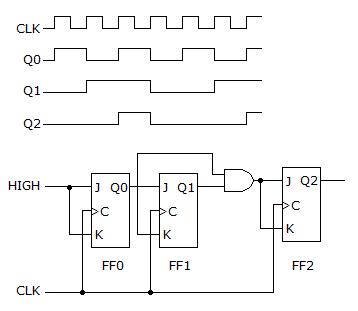

- 2. A four-channel scope is used to check the counter in the figure given below. Are the displayed waveforms correct?

Options- A. Yes

- B. No Discuss

- 3. After 10 clock cycles, and assuming that the DATA input had returned to 0 following the storage sequence, what values would be stored in Q4, Q3, Q2, Q1, Q0 of the register in Figure 7-5?

Options- A. 0,1,0,1,1

- B. 1,1,0,1,0

- C. 1,0,1,0,1

- D. 0,0,0,0,0 Discuss

- 4. What type of device is shown below?

Options- A. 4-bit bidirectional universal shift register

- B. Parallel in/parallel out shift register with bidirectional data flow

- C. 2-way parallel in/serial out bidirectional register

- D. 2-bit serial in/4-bit parallel out bidirectional shift register Discuss

- 5. Using four cascaded counters with a total of 16 bits, how many states must be deleted to achieve a modulus of 50,000?

Options- A. 50,000

- B. 65,536

- C. 25,536

- D. 15,536 Discuss

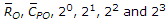

- 6. The designation

means that the ________.

means that the ________.

Options- A. up count is active-HIGH, the down count is active-LOW

- B. up count is active-LOW, the down count is active-HIGH

- C. up and down counts are both active-LOW

- D. up and down counts are both active-HIGH Discuss

- 7. How many flip-flops are required to make a MOD-32 binary counter?

Options- A. 3

- B. 45

- C. 5

- D. 6 Discuss

- 8. A MOD-16 synchronous counter has inputs labeled

. These inputs would most probably be used to:

. These inputs would most probably be used to:

Options- A. reset the counter to 0000 at the end of each count cycle

- B. preset the counter to a value determined by the

inputs any time the

inputs any time the  is active-HIGH

is active-HIGH - C. preset the counter to a value determined by the

inputs any time the

inputs any time the  is active-LOW

is active-LOW - D. reset the counter to 0000 any time

is active-HIGH and

is active-HIGH and  is active-LOW

Discuss

is active-LOW

Discuss

- 9. Which segments of a seven-segment display would be required to be active to display the decimal digit 2?

Options- A. a, b, d, e, and g

- B. a, b, c, d, and g

- C. a, c, d, f, and g

- D. a, b, c, d, e, and f Discuss

- 10. Which of the following groups of logic devices would be the minimum required for a MOD-64 synchronous counter?

Options- A. Five flip-flops, three AND gates

- B. Seven flip-flops, five AND gates

- C. Four flip-flops, ten AND gates

- D. Six flip-flops, four AND gates Discuss

Counters problems

Search Results

Correct Answer: 125

Correct Answer: No

Correct Answer: 0,0,0,0,0

Correct Answer: 4-bit bidirectional universal shift register

Correct Answer: 15,536

Correct Answer: up count is active-HIGH, the down count is active-LOW

Correct Answer: 5

Correct Answer: reset the counter to 0000 any time

is active-HIGH and

is active-HIGH and  is active-LOW

is active-LOW Correct Answer: a, b, d, e, and g

Correct Answer: Six flip-flops, four AND gates

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.