Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Circuits Comments

- Question

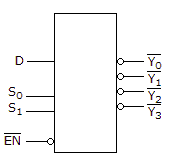

For the device shown here, assume the D input is LOW, both S inputs are HIGH, and the

input is HIGH. What is the status of the

input is HIGH. What is the status of the  outputs?

outputs?

Options- A. All are HIGH.

- B. All are LOW.

- C. All but

are LOW.

are LOW. - D. All but

are HIGH.

are HIGH. - Correct Answer

- All are HIGH.

- 1. How many data select lines are required for selecting eight inputs?

Options- A. 1

- B. 2

- C. 3

- D. 4 Discuss

- 2. Convert BCD 0001 0010 0110 to binary.

Options- A. 1111110

- B. 1111101

- C. 1111000

- D. 1111111 Discuss

- 3. What will a design engineer do after he/she is satisfied that the design will work?

Options- A. Put it in a flow chart

- B. Program a chip and test it

- C. Give the design to a technician to verify the design

- D. Perform a vector test Discuss

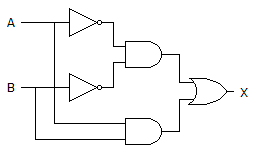

- 4. What type of logic circuit is represented by the figure shown below?

Options- A. XOR

- B. XNOR

- C. XAND

- D. XNAND Discuss

- 5. In VHDL, macrofunctions is/are:

Options- A. digital circuits.

- B. analog circuits.

- C. a set of bit vectors.

- D. preprogrammed TTL devices. Discuss

- 6. How many 4-bit parallel adders would be required to add two binary numbers each representing decimal numbers up through 30010?

Options- A. 1

- B. 2

- C. 3

- D. 4 Discuss

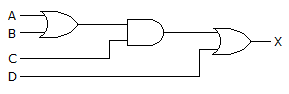

- 7. Solve the network in the figure given below for X.

Options- A. A + BC + D

- B. ((A + B)C) + D

- C. D(A + B + C)

- D. (AC + BC)D Discuss

- 8. As a technician you are confronted with a TTL circuit board containing dozens of IC chips. You have taken several readings at numerous IC chips, but the readings are inconclusive because of their erratic nature. Of the possible faults listed, select the one that most probably is causing the problem.

Options- A. A defective IC chip that is drawing excessive current from the power supply

- B. A solar bridge between the inputs on the first IC chip on the board

- C. An open input on the first IC chip on the board

- D. A defective output IC chip that has an internal open to Vcc Discuss

- 9. What is the indication of a short on the input of a load gate?

Options- A. Only the output of the defective gate is affected.

- B. There is a signal loss to all gates on the node.

- C. The affected node will be stuck in the LOW state.

- D. There is a signal loss to all gates on the node, and the affected node will be stuck in the LOW state. Discuss

- 10. For the device shown here, assume the D input is LOW, both S inputs are LOW, and the

input is LOW. What is the status of the

input is LOW. What is the status of the  outputs?

outputs?

Options- A. All are HIGH.

- B. All are LOW.

- C. All but

are LOW.

are LOW. - D. All but

are HIGH.

Discuss

are HIGH.

Discuss

Combinational Logic Circuits problems

Search Results

Correct Answer: 3

Correct Answer: 1111110

Correct Answer: Program a chip and test it

Correct Answer: XNOR

Correct Answer: preprogrammed TTL devices.

Correct Answer: 3

Correct Answer: ((A + B)C) + D

Correct Answer: An open input on the first IC chip on the board

Correct Answer: There is a signal loss to all gates on the node, and the affected node will be stuck in the LOW state.

Correct Answer: All but

are HIGH.

are HIGH. Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.