Discussion

Home ‣ Digital Electronics ‣ Flip-Flops See What Others Are Saying!

- Question

A gated S-R flip-flop goes into the CLEAR condition when ________.

Options- A. S is HIGH; R is LOW; EN is HIGH

- B. S is LOW; R is HIGH; EN is HIGH

- C. S is LOW; R is HIGH; EN is LOW

- D. S is HIGH; R is LOW; EN is LOW

- Correct Answer

- S is LOW; R is HIGH; EN is HIGH

- 1. How many gates would be required to implement the following Boolean expression before simplification? XY + X(X + Z) + Y(X + Z)

Options- A. 1

- B. 2

- C. 4

- D. 5 Discuss

- 2. The 7447A is a BCD-to-7-segment decoder with ripple blanking input and output functions. The purpose of these lines is to ________.

Options- A. turn off the display for any nonsignificant digit

- B. turn off the display for any zero

- C. turn off the display for leading or trailing zeros

- D. test the display to assure all segments are operational Discuss

- 3. In an even-parity system, the following data will produce a parity bit = 1.

data = 1010011

Options- A. True

- B. False Discuss

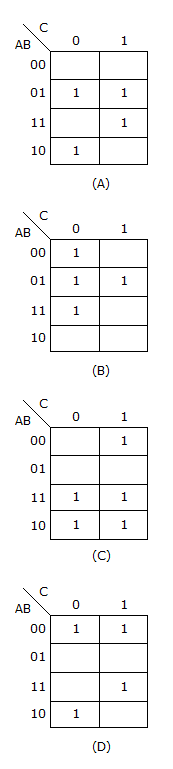

- 4. Mapping the SOP expression

, we get ________.

, we get ________.

Options- A. (A)

- B. (B)

- C. (C)

- D. (D) Discuss

- 5. In the digital clock project, the AHDL block codes are connected using graphic design files.

Options- A. True

- B. False Discuss

- 6. The main advantage of semiconductor RAM is its ability to:

Options- A. retain stored data when power is interrupted or turned off

- B. be written to and read from rapidly

- C. be randomly accessed

- D. be sequentially accessed Discuss

- 7. The binary number for octal 458 is ________.

Options- A. 100010

- B. 100101

- C. 110101

- D. 100100 Discuss

- 8. Which of the following instructions will move the contents of the accumulator to register 6?

Options- A. MOV 6R, A

- B. MOV R6, A

- C. MOV A, 6R

- D. MOV A, R6 Discuss

- 9. Because of their nonvolatility, high speed, low power requirements, and lack of moving parts, ________ have become feasible alternatives to magnetic disk storage.

Options- A. CD-ROMs

- B. flash memory modules

- C. ROMs

- D. EPROMs Discuss

- 10. What two functions does a DRAM controller perform?

Options- A. address multiplexing and data selection

- B. address multiplexing and the refresh operation

- C. data selection and the refresh operation

- D. data selection and CPU accessing Discuss

More questions

Correct Answer: 5

Correct Answer: turn off the display for any nonsignificant digit

Correct Answer: False

Correct Answer: (B)

Correct Answer: True

Correct Answer: be written to and read from rapidly

Correct Answer: 100101

Correct Answer: MOV R6, A

Correct Answer: flash memory modules

Correct Answer: address multiplexing and the refresh operation

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.