Discussion

Home ‣ Digital Electronics ‣ Flip-Flops See What Others Are Saying!

- Question

Pulse-triggered flip-flops are identified by a bubble on the Q output terminal.

Options- A. True

- B. False

- Correct Answer

- False

- 1. The DAC0808 and the MC1408 are very popular and inexpensive 8-bit D/A converters.

Options- A. True

- B. False Discuss

- 2. What is the advantage of using CMOS logic over TTL?

Options- A. It switches faster.

- B. It uses less power.

- C. It is larger.

- D. cost Discuss

- 3. A logic signal experiences a delay in going through a circuit. The two propagation delay times are defined as:

Options- A. tPLH and tPHL.

- B. tDLH and tDHL.

- C. tHPL and tlph.

- D. tLDH and tHDL. Discuss

- 4. Serial communications cannot be sped up.

Options- A. True

- B. False Discuss

- 5. If all inputs to a TTL NAND gate are low, what is the ON, OFF condition of each transistor in the circuit?

Options- A. Q1-ON, Q2-OFF, Q3-ON, Q4-OFF

- B. Q1-ON, Q2-ON, Q3-OFF, Q4-OFF

- C. Q1-OFF, Q2-OFF, Q3-ON, Q4-ON

- D. Q1-OFF, Q2-ON, Q3-OFF, Q4-ON Discuss

- 6. When the output of a standard TTL gate is HIGH, it can ________.

Options- A. sink 16 mA of current from the attached input gates

- B. source 400 µA of current to no more than 10 attached gates

- C. source 16 mA of current to no more than 10 attached gates

- D. sink a maximum of 400 µA from no more than 10 load gates Discuss

- 7. The equation ________ cannot be further simplified.

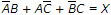

Options- A.

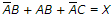

- B.

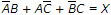

- C.

- D.

Discuss

Discuss

- 8. Assume that a particular IC has a supply voltage (Vcc) equal to +5 V and ICCH = 10 mA and ICCL = 23 mA. What is the power dissipation for the chip?

Options- A. 50 mW

- B. 82.5 mW

- C. 115 mW

- D. 165 mW Discuss

- 9. LDA addr and STA addr are Fortran language instructions stored in an external memory IC for a microprocessor.

Options- A. True

- B. False Discuss

- 10. A(n) ________ is a section of embedded logic that is commonly found in FPGAs.

Options- A. LUT

- B. core

- C. DSP

- D. PI Discuss

More questions

Correct Answer: True

Correct Answer: It uses less power.

Correct Answer: tPLH and tPHL.

Correct Answer: False

Correct Answer: Q1-ON, Q2-OFF, Q3-ON, Q4-OFF

Correct Answer: source 400 µA of current to no more than 10 attached gates

Correct Answer:

Correct Answer: 82.5 mW

Correct Answer: False

Correct Answer: core

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.