Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Circuits Comments

- Question

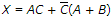

The simplified form of

is ________.

is ________.

Options- A.

- B.

- C.

- D.

- Correct Answer

- 1. When grouping cells within a K-map, the cells must be combined in groups of ________.

Options- A. 2's

- B. 1, 2, 4, 8, etc.

- C. 4's

- D. 3's Discuss

- 2. The ________ series of IC's are pin, function, and voltage-level compatible with the 74 series IC's.

Options- A. ALS

- B. CMOS

- C. HCT

- D. 2N Discuss

- 3. The ________ circuit produces a HIGH output whenever the two inputs are unequal.

Options- A. exclusive-AND

- B. exclusive-NOR

- C. exclusive-OR

- D. inexclusive-OR Discuss

- 4. A gate that could be used to compare two logic levels and provide a HIGH output if they are equal is a(n) ________.

Options- A. XOR gate

- B. XNOR gate

- C. NAND gate

- D. NOR gate Discuss

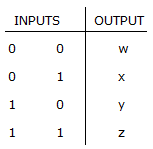

- 5. For the XNOR gate truth table shown below, the values for w, x, y, and z are ____, ____, ____, and ____, respectively.

Options- A. 1, 0, 0, 1

- B. 0, 1, 0, 1

- C. 1, 1, 1, 0

- D. 1, 0, 0, 0 Discuss

- 6. One reason for using the sum-of-products form is that it can be implemented using all ________ gates without much difficulty.

Options- A. NOR

- B. NAND

- C. AND

- D. DOOR Discuss

- 7. The output of a gate has an internal short; a current tracer will ________.

Options- A. identify the defective gate

- B. show whether the gate is shorted to Vcc or ground

- C. probably not be able to locate the problem

- D. be able to identify the defective load node Discuss

- 8. The largest truth table that can be implemented directly with an 8-line-to-1-line MUX has ________.

Options- A. 3 rows

- B. 4 rows

- C. 8 rows

- D. 16 rows Discuss

- 9. When an open occurs on the input of a CMOS gate, the output will ________.

Options- A. go LOW, because there is no current in an open circuit

- B. react as if the open input were a HIGH

- C. go HIGH, since full voltage appears across an open

- D. be unpredictable; it may go HIGH or LOW Discuss

- 10. VHDL is very strict in the way it allows us to assign and compare ________ such as signals, variables, constants, and literals.

Options- A. objects

- B. LOGIC_VECTORS

- C. designs

- D. arrays Discuss

Combinational Logic Circuits problems

Search Results

Correct Answer: 1, 2, 4, 8, etc.

Correct Answer: HCT

Correct Answer: exclusive-OR

Correct Answer: XNOR gate

Correct Answer: 1, 0, 0, 1

Correct Answer: NAND

Correct Answer: identify the defective gate

Correct Answer: 8 rows

Correct Answer: be unpredictable; it may go HIGH or LOW

Correct Answer: objects

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.