Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Circuits See What Others Are Saying!

- Question

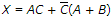

The simplified form of

is ________.

is ________.

Options- A.

- B.

- C.

- D.

- Correct Answer

- 1. A NAND gate output is LOW only if all the inputs are HIGH.

Options- A. True

- B. False Discuss

- 2. Edge-triggered flip-flops can be identified by the triangle on the clock input.

Options- A. True

- B. False Discuss

- 3. How many select lines would be required for an 8-line-to-1-line multiplexer?

Options- A. 2

- B. 3

- C. 4

- D. 8 Discuss

- 4. A(n)________ is not a functional unit of a computer.

Options- A. input unit

- B. memory unit

- C. modem

- D. control unit Discuss

- 5. A modulus-12 ring counter requires a minimum of ________.

Options- A. 10 flip-flops

- B. 12 flip-flops

- C. 6 flip-flops

- D. 2 flip-flops Discuss

- 6. Which is not characteristic of a shift register?

Options- A. Serial in/parallel in

- B. Serial in/parallel out

- C. Parallel in/serial out

- D. Parallel in/parallel out Discuss

- 7. The base of the hexadecimal system is:

Options- A. eight.

- B. sixteen.

- C. ten.

- D. two. Discuss

- 8. Hexadecimal is a base 4 numbering system.

Options- A. True

- B. False Discuss

- 9. How many inputs must a full-adder have?

Options- A. 2

- B. 3

- C. 4

- D. 5 Discuss

- 10. In a negative logic system, a high is represented by 0.

Options- A. True

- B. False Discuss

More questions

Correct Answer: True

Correct Answer: True

Correct Answer: 3

Correct Answer: modem

Correct Answer: 12 flip-flops

Correct Answer: Serial in/parallel in

Correct Answer: sixteen.

Correct Answer: False

Correct Answer: 3

Correct Answer: True

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.