Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Circuits Comments

- Question

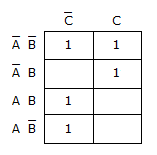

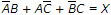

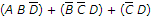

The Boolean equation ________ results from this Karnaugh map.

Options- A.

- B.

- C.

- D.

- Correct Answer

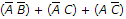

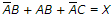

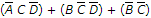

- 1. The equation ________ cannot be further simplified.

Options- A.

- B.

- C.

- D.

Discuss

Discuss

- 2. Occasionally, a particular logic expression will be of no consequence in the operation of a circuit, such as in a BCD-to-decimal converter. These result in ________ terms in the K-map and can be treated as either ________ or ________, in order to ________ the resulting term.

Options- A. don't care, 1's, 0's, simplify

- B. spurious, AND's, OR's, eliminate

- C. duplicate, 1's, 0's, verify

- D. spurious, 1's, 0's, simplify Discuss

- 3. A half-adder does not have ________.

Options- A. carry in

- B. carry out

- C. two inputs

- D. all of the above Discuss

- 4. When an open occurs on the input of a TTL device, the output will ________.

Options- A. go LOW, because there is no current in an open circuit

- B. react as if the open input were a HIGH

- C. go HIGH, since full voltage appears across an open

- D. still be good, if only the good inputs are used Discuss

- 5. Parity generators and checkers use ________ gates.

Options- A. exclusive-AND

- B. exclusive-OR/NOR

- C. exclusive-OR

- D. exclusive-NAND Discuss

- 6. Two 4-bit comparators are cascaded to form an 8-bit comparator. The cascading inputs of the most significant 4 bits should be connected ________.

Options- A. to the outputs from the least significant 4-bit comparator

- B. to the cascading inputs of the least significant 4-bit comparator

- C. A = B to a logic high, A < b and a > B to a logic low

- D. ground Discuss

- 7. The AND-OR-INVERT gates are designed to simplify implementation of ________.

Options- A. POS logic

- B. DeMorgan's theorem

- C. NAND logic

- D. SOP logic Discuss

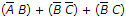

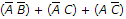

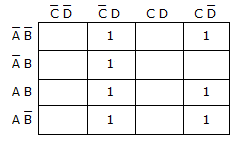

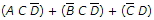

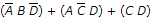

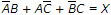

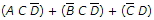

- 8. The Boolean equation ________ results from this Karnaugh map.

Options- A.

- B.

- C.

- D.

Discuss

Discuss

- 9. The final output of a POS circuit is generated by ________.

Options- A. an AND

- B. an OR

- C. a NOR

- D. a NAND Discuss

- 10. When Karnaugh mapping, we must be sure to use the ________ number of loops.

Options- A. maximum

- B. minimum

- C. median

- D. Karnaugh Discuss

Combinational Logic Circuits problems

Search Results

Correct Answer:

Correct Answer: don't care, 1's, 0's, simplify

Correct Answer: carry in

Correct Answer: react as if the open input were a HIGH

Correct Answer: exclusive-OR/NOR

Correct Answer: to the outputs from the least significant 4-bit comparator

Correct Answer: DeMorgan's theorem

Correct Answer:

Correct Answer: an AND

Correct Answer: minimum

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.