Discussion

Home ‣ Digital Electronics ‣ Logic Gates See What Others Are Saying!

- Question

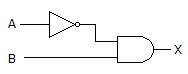

The gates in this figure are implemented using TTL logic. If the input of the inverter is open, and you apply logic pulses to point B, the output of the AND gate will be ________.

Options- A. a steady LOW

- B. a steady HIGH

- C. an undefined level

- D. pulses

- Correct Answer

- a steady LOW

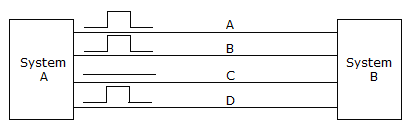

- 1. The systems shown in the given figure communicate using ________.

Options- A. parallel data

- B. serial data

- C. serial-parallel data

- D. both parallel and serial data Discuss

- 2. The special function registers can be referred to by their hex addresses or by their register names.

Options- A. True

- B. False Discuss

- 3. A D/A converter changes things such as temperature variations into digital quantities.

Options- A. True

- B. False Discuss

- 4. The SO package is available for the most popular TTL and CMOS digital logic and analog IC devices.

Options- A. True

- B. False Discuss

- 5. What is the difference between a 7490 and a 7493?

Options- A. 7490 is a MOD-10, 7493 is a MOD-16

- B. 7490 is a MOD-16, 7493 is a MOD-10

- C. 7490 is a MOD-12, 7493 is a MOD-16

- D. 7490 is a MOD-10, 7493 is a MOD-12 Discuss

- 6. A 4-bit binary up counter has an input clock frequency of 20 kHz. The frequency of the most significant bit is ________.

Options- A. 1.25 kHz

- B. 2.50 kHz

- C. 160 kHz

- D. 320 kHz Discuss

- 7. Inaccurate A/D conversion may be due to:

Options- A. constant analog input voltage

- B. linear ramp usage

- C. intermittent counter inputs

- D. faulty sample-and-hold circuitry Discuss

- 8. All outputs of the 74138 octal decoder are disabled (HIGH) when the enable inputs are:

Options- A. True

- B. False Discuss

- 9. In HDL when a circuit is simulated on a computer, the designer must create all the different scenarios that will be experienced by the actual circuit and must also know the proper response to those inputs.

Options- A. True

- B. False Discuss

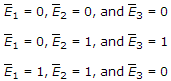

- 10. The designation

means that the ________.

means that the ________.

Options- A. up count is active-HIGH, the down count is active-LOW

- B. up count is active-LOW, the down count is active-HIGH

- C. up and down counts are both active-LOW

- D. up and down counts are both active-HIGH Discuss

More questions

Correct Answer: parallel data

Correct Answer: True

Correct Answer: False

Correct Answer: True

Correct Answer: 7490 is a MOD-10, 7493 is a MOD-16

Correct Answer: 1.25 kHz

Correct Answer: faulty sample-and-hold circuitry

Correct Answer: True

Correct Answer: True

Correct Answer: up count is active-HIGH, the down count is active-LOW

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.