Discussion

Home ‣ Digital Electronics ‣ Digital System Projects Using HDL See What Others Are Saying!

- Question

In the digital clock project, when does the PM indicator go high?

Options- A. Never

- B. Going from 11:59:59 to 12:00:00

- C. Going from 12:59:59 to 01:00:00

- D. On the falling edge of the clock after enable goes high

- Correct Answer

- Going from 11:59:59 to 12:00:00

- 1. Three cascaded modulus-10 counters have an overall modulus of 1000.

Options- A. True

- B. False Discuss

- 2. Convert each of the decimal numbers to two's-complement form and perform the addition in binary.

+13 ?10 add ?7 add +15

Options- A. 0001 0100 0000 0101

- B. 0000 0110 0001 1001

- C. 0000 0110 0000 0101

- D. 1111 0110 1111 0101 Discuss

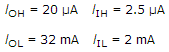

- 3. From the following specifications determine the fan-out for the logic family.

Options- A. HIGH state is 16, LOW state is 8

- B. HIGH state is 8, LOW state is 16

- C. HIGH state is 4, LOW state is 8

- D. HIGH state is 8, LOW state is 4 Discuss

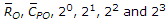

- 4. A MOD-16 synchronous counter has inputs labeled

. These inputs would most probably be used to:

. These inputs would most probably be used to:

Options- A. reset the counter to 0000 at the end of each count cycle

- B. preset the counter to a value determined by the

inputs any time the

inputs any time the  is active-HIGH

is active-HIGH - C. preset the counter to a value determined by the

inputs any time the

inputs any time the  is active-LOW

is active-LOW - D. reset the counter to 0000 any time

is active-HIGH and

is active-HIGH and  is active-LOW

Discuss

is active-LOW

Discuss

- 5. Generally, a flip-flop's hold time is short enough so that its output will go to a state determined by the logic levels present at its synchronous control inputs just prior to the active clock transition.

Options- A. True

- B. False Discuss

- 6. The device that is an application of SOP logic is a multiplexer.

Options- A. True

- B. False Discuss

- 7. In AHDL macrofunctions, the first thing that should go into any source file is ________ your code.

Options- A. a field of comments that documents

- B. a library of

- C. a function name of

- D. the universal global definition of Discuss

- 8. Using the universal property of a NAND gate, one or more NAND gates can be used to replace an ________.

Options- A. OR gate

- B. AND gate

- C. inverter

- D. any of the above Discuss

- 9. During a memory read operation, the CPU fetches ________.

Options- A. a program instruction

- B. an address

- C. data

- D. all of the above Discuss

- 10. ________ is ideally suited for applications using battery power or battery backup power.

Options- A. MOS

- B. P-MOS

- C. N-MOS

- D. CMOS Discuss

More questions

Correct Answer: True

Correct Answer: 0000 0110 0000 0101

Correct Answer: HIGH state is 8, LOW state is 16

Correct Answer: reset the counter to 0000 any time

is active-HIGH and

is active-HIGH and  is active-LOW

is active-LOW Correct Answer: True

Correct Answer: True

Correct Answer: a field of comments that documents

Correct Answer: any of the above

Correct Answer: all of the above

Correct Answer: CMOS

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.