Discussion

Home ‣ Digital Electronics ‣ Counters See What Others Are Saying!

- Question

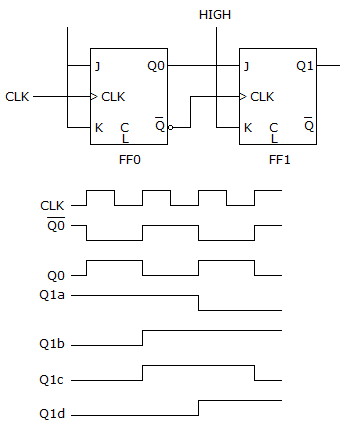

The circuit given below has no output on Q1 when examined with an oscilloscope. All J-K inputs are HIGH, the CLK signal is present, and the Q0 is toggling. The C input of FF1 is a constant LOW. What could be causing the problem?

Options- A. The Q0 output should be connected to the J input of FF1.

- B. The output of FF0 may be shorted to ground.

- C. The input of FF1 may be shorted to ground.

- D. Either the output of FF0 or the input of FF1 may be shorted to ground.

- Correct Answer

- Either the output of FF0 or the input of FF1 may be shorted to ground.

- 1. A 1-of-8 octal decoder has eight outputs and decodes an input of ________ bit(s).

Options- A. three

- B. two

- C. four

- D. one Discuss

- 2. A four-line multiplexer must have as inputs four data inputs and two select inputs.

Options- A. True

- B. False Discuss

- 3. Basically, a multiplexer changes parallel data inputs to a serial output.

Options- A. True

- B. False Discuss

- 4. In a positive logic system, the HIGH level is usually represented by ________.

Options- A. 0 V

- B. +1 V

- C. +5 V

- D. +9 V Discuss

- 5. Eight bits of digital data are normally referred to as a:

Options- A. group.

- B. byte.

- C. word.

- D. cell. Discuss

- 6. The JTAG signals are named TDI, TDO, TMS, and TCK.

Options- A. True

- B. False Discuss

- 7. The exclusive-OR provides a LOW input if one input or the other input is HIGH.

Options- A. True

- B. False Discuss

- 8. A burst refresh and a normal memory operation of a DRAM can be interspersed.

Options- A. True

- B. False Discuss

- 9. When extremely critical timing is required, a quartz crystal can be used.

Options- A. True

- B. False Discuss

- 10. How many 2K × 8 ROM chips would be required to build a 16K × 8 memory system?

Options- A. 2

- B. 4

- C. 8

- D. 16 Discuss

More questions

Correct Answer: three

Correct Answer: True

Correct Answer: True

Correct Answer: +5 V

Correct Answer: byte.

Correct Answer: True

Correct Answer: False

Correct Answer: False

Correct Answer: True

Correct Answer: 8

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.