Discussion

Home ‣ Digital Electronics ‣ Counters See What Others Are Saying!

- Question

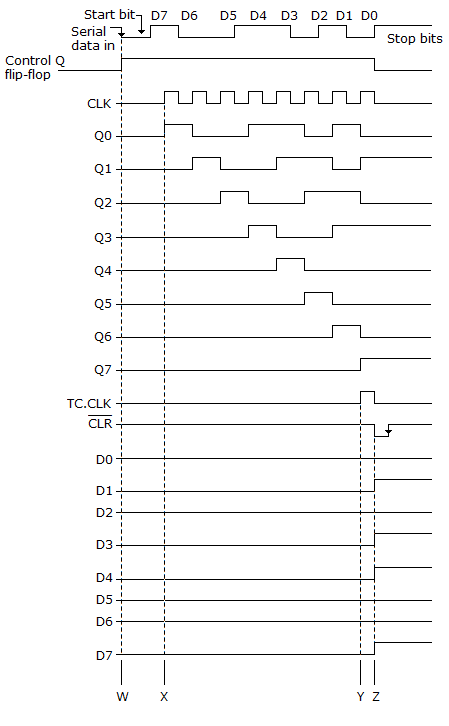

Referring to the given figure, what causes the Control FF to reset after D7?

Options- A. Once the data cycle is initiated by the Start bit, the one-shot produces an output pulse equal to the duration of the eight data bits. Once the eight data bits have been transferred to the data input register, the falling edge of the one-shot pulse resets the Control FF to start the sequence all over again.

- B. After counting the eight data bits, the divide-by-8 counter produces an output on its active-LOW CLR line to reset the Control FF.

- C. After counting eight clock pulses equivalent to eight data periods, the terminal count of the divide-by-8 counter and the clock trigger the one-shot, which in turn resets the Control FF and divide-by-8 circuits to begin the sequence all over again. Simultaneously the data is transferred through the output register.

- D. When the data output register is full, it produces an output on its C terminal that triggers the one-shot, which in turn resets the Control FF.

- Correct Answer

- After counting eight clock pulses equivalent to eight data periods, the terminal count of the divide-by-8 counter and the clock trigger the one-shot, which in turn resets the Control FF and divide-by-8 circuits to begin the sequence all over again. Simultaneously the data is transferred through the output register.

- 1. Propagation delay is important because ________.

Options- A. the logic gates must be given a short break during each clock cycle or else they will overheat

- B. it limits the maximum operating frequency of a gate

- C. it is a measure of how long the clock must be applied to the gate before it will make the required decision

- D. all the gates in a system must have the same propagation times in order to be compatible Discuss

- 2. The carry propagation can be expressed as ________.

Options- A. Cp = AB

- B. Cp = A + B

- C.

- D.

Discuss

Discuss

- 3. The odd/even parity system would require a sixth bit to be added to a 4-bit system.

Options- A. True

- B. False Discuss

- 4. In a digital storage scope, when memory is full, the next data point is lost.

Options- A. True

- B. False Discuss

- 5. A D flip-flop utilizing a PGT clock is in the CLEAR state. Which of the following input actions will cause it to change states?

Options- A. CLK = NGT, D = 0

- B. CLK = PGT, D = 0

- C. CLOCK NGT, D = 1

- D. CLOCK PGT, D = 1

- E. CLK = NGT, D = 0, CLOCK NGT, D = 1 Discuss

- 6. What is the difference between combinational logic and sequential logic?

Options- A. Combinational circuits are not triggered by timing pulses, sequential circuits are triggered by timing pulses.

- B. Combinational and sequential circuits are both triggered by timing pulses.

- C. Neither circuit is triggered by timing pulses. Discuss

- 7. There are four different logic level ranges for TTL and CMOS: VIL, VIH, VOL, and VOH.

Options- A. True

- B. False Discuss

- 8. One method of troubleshooting involves ________ the circuit under test with a ________ or ________ and then observing the output to check for proper bit patterns.

Options- A. checking, voltmeter, ohmmeter

- B. exercising, stimulus, test pattern

- C. testing, scope, logic analyzer

- D. smashing, hammer, axe Discuss

- 9. A demultiplexer is a device that converts some code to a recognizable number or character.

Options- A. True

- B. False Discuss

- 10. What distinguishes the look-ahead-carry adder?

Options- A. It is slower than the ripple-carry adder.

- B. It is easier to implement logically than a full adder.

- C. It is faster than a ripple-carry adder.

- D. It requires advance knowledge of the final answer. Discuss

More questions

Correct Answer: the logic gates must be given a short break during each clock cycle or else they will overheat

Correct Answer: Cp = A + B

Correct Answer: False

Correct Answer: False

Correct Answer: CLOCK PGT, D = 1

Correct Answer: Combinational circuits are not triggered by timing pulses, sequential circuits are triggered by timing pulses.

Correct Answer: True

Correct Answer: exercising, stimulus, test pattern

Correct Answer: False

Correct Answer: It is faster than a ripple-carry adder.

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.