Discussion

Home ‣ Digital Electronics ‣ Counters Comments

- Question

Once an up-/down-counter begins its count sequence, it cannot be reversed.

Options- A. True

- B. False

- Correct Answer

- False

- 1. MOD-6 and MOD-12 counters and multiples are most commonly used as:

Options- A. frequency counters

- B. multiplexed displays

- C. digital clocks

- D. power consumption meters Discuss

- 2. How many different states does a 3-bit asynchronous counter have?

Options- A. 2

- B. 4

- C. 8

- D. 16 Discuss

- 3. What is the maximum delay that can occur if four flip-flops are connected as a ripple counter and each flip-flop has propagation delays of tPHL = 22 ns and tPLH = 15 ns?

Options- A. 15 ns

- B. 22 ns

- C. 60 ns

- D. 88 ns Discuss

- 4. Which is not an example of a truncated modulus?

Options- A. 8

- B. 9

- C. 11

- D. 15 Discuss

- 5. Which of the following statements are true?

Options- A. Asynchronous events do not occur at the same time.

- B. Asynchronous events are controlled by a clock.

- C. Synchronous events do not need a clock to control them.

- D. Only asynchronous events need a control clock. Discuss

- 6. A MOD-16 ripple counter is holding the count 10012. What will the count be after 31 clock pulses?

Options- A. 10002

- B. 10102

- C. 10112

- D. 11012 Discuss

- 7. A principle regarding most display decoders is that when the correct input is present, the related output will switch:

Options- A. HIGH

- B. to high impedance

- C. to an open

- D. LOW Discuss

- 8. Synchronous (parallel) counters eliminate the delay problems encountered with asynchronous (ripple) counters because the:

Options- A. input clock pulses are applied only to the first and last stages.

- B. input clock pulses are applied only to the last stage.

- C. input clock pulses are applied simultaneously to each stage.

- D. input clock pulses are not used to activate any of the counter stages. Discuss

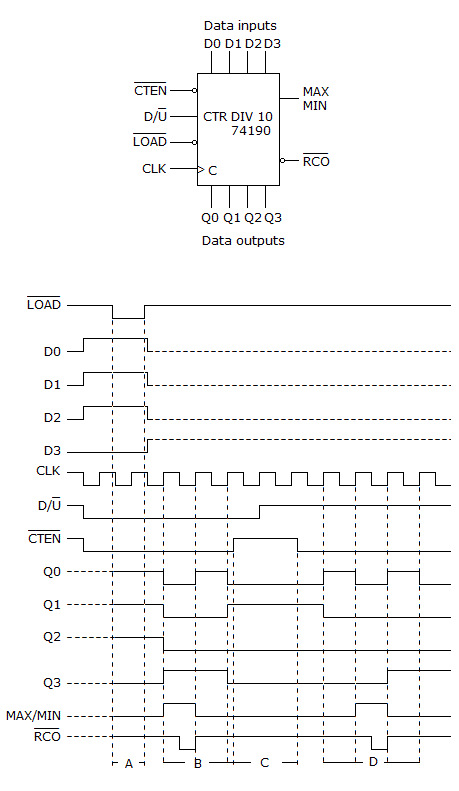

- 9. What function will the counter shown below be performing during period "B" on the timing diagram?

Options- A. Counting up

- B. Counting down

- C. Inhibited

- D. Loading Discuss

- 10. Any divide-by-N counter can be formed by using external gating to ________ at a predetermined number.

Options- A. HIGH

- B. reset

- C. LOW

- D. preset Discuss

Counters problems

Search Results

Correct Answer: digital clocks

Correct Answer: 8

Correct Answer: 88 ns

Correct Answer: 8

Correct Answer: Asynchronous events do not occur at the same time.

Correct Answer: 10002

Correct Answer: LOW

Correct Answer: input clock pulses are applied simultaneously to each stage.

Correct Answer: Counting up

Correct Answer: reset

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.