Discussion

Home ‣ Digital Electronics ‣ Counters See What Others Are Saying!

- Question

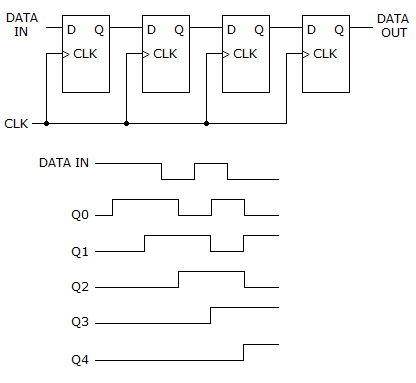

How many data bits can be stored in the register shown below?

Options- A. 5

- B. 32

- C. 31

- D. 4

- Correct Answer

- 5

- 1. A VHDL component is a predefined logic function.

Options- A. True

- B. False Discuss

- 2. L1 is known as ________.

Options- A. primary cache

- B. secondary cache

- C. DRAM

- D. SRAM Discuss

- 3. All inputs to the MAX7000S device and all macrocell outputs feed the PIA.

Options- A. True

- B. False Discuss

- 4. The 74154 is a 1-of-16 decoder. It accepts a 4-bit binary input.

Options- A. True

- B. False Discuss

- 5. A 1-of-8 octal decoder has eight outputs and decodes an input of ________ bit(s).

Options- A. three

- B. two

- C. four

- D. one Discuss

- 6. A four-line multiplexer must have as inputs four data inputs and two select inputs.

Options- A. True

- B. False Discuss

- 7. Basically, a multiplexer changes parallel data inputs to a serial output.

Options- A. True

- B. False Discuss

- 8. In a positive logic system, the HIGH level is usually represented by ________.

Options- A. 0 V

- B. +1 V

- C. +5 V

- D. +9 V Discuss

- 9. Eight bits of digital data are normally referred to as a:

Options- A. group.

- B. byte.

- C. word.

- D. cell. Discuss

- 10. The JTAG signals are named TDI, TDO, TMS, and TCK.

Options- A. True

- B. False Discuss

More questions

Correct Answer: False

Correct Answer: primary cache

Correct Answer: True

Correct Answer: True

Correct Answer: three

Correct Answer: True

Correct Answer: True

Correct Answer: +5 V

Correct Answer: byte.

Correct Answer: True

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.