Discussion

Home ‣ Digital Electronics ‣ Flip-Flops See What Others Are Saying!

- Question

In VHDL, how many inputs will a primitive JK flip-flop have?

Options- A. 2

- B. 3

- C. 4

- D. 5

- Correct Answer

- 5

- 1. If a typical PC uses a 20-bit address code, how much memory can the CPU address?

Options- A. 20 MB

- B. 10 MB

- C. 1 MB

- D. 580 MB Discuss

- 2. Circuits that exhibit the property of memory normally revert to their original state when the input is removed.

Options- A. True

- B. False Discuss

- 3. GAL is an acronym for ________.

Options- A. Generic Array Logic

- B. General Array Logic

- C. Giant Array Logic

- D. Generic Analysis Logic Discuss

- 4. The output of a standard TTL NAND gate is used to pull an LED indicator LOW. The LED is in series with a 470-Ω resistor. What is the current in the circuit when the LED is on?

Options- A. 7.02 mA

- B. 8.51 mA

- C. 10.63 mA

- D. 5.32 mA Discuss

- 5. What would be the output voltage of a 7814 voltage regulator?

Options- A. ?14 V dc

- B. +14 V dc

- C. ?8 V dc

- D. +8 V dc Discuss

- 6. If the least significant bit (LSB) of a four-bit binary-weighted resistor D/A converter connects to a 200 Ω resistor, then the resistor needed for the next bit is 100 Ω.

Options- A. True

- B. False Discuss

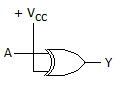

- 7. The output of this circuit is always ________.

Options- A. 1

- B. 0

- C. A

- D. A Discuss

- 8. DRAM chips can be combined for larger capacity and word sizes using the same methods as for other memory types.

Options- A. True

- B. False Discuss

- 9. Flash A/D converters depend on an input clock pulse to perform each conversion.

Options- A. True

- B. False Discuss

- 10. Electrical noise does not affect the transmission of binary information.

Options- A. True

- B. False Discuss

More questions

Correct Answer: 1 MB

Correct Answer: False

Correct Answer: Generic Array Logic

Correct Answer: 7.02 mA

Correct Answer: +14 V dc

Correct Answer: True

Correct Answer: A

Correct Answer: True

Correct Answer: False

Correct Answer: False

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.