Discussion

Home ‣ Digital Electronics ‣ Flip-Flops See What Others Are Saying!

- Question

A J-K flip-flop is in a "no change" condition when ________.

Options- A. J = 1, K = 1

- B. J = 1, K = 0

- C. J = 0, K = 1

- D. J = 0, K = 0

- Correct Answer

- J = 0, K = 0

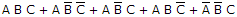

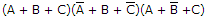

- 1. The Boolean expression for the logic circuit shown is _____.

Options- A.

- B.

- C.

- D.

Discuss

Discuss

- 2. In the VHDL code of the stepper motor, the cout outputs are bit_vector type because they are binary bit patterns.

Options- A. True

- B. False Discuss

- 3. The term race condition describes the time that an active signal must be present at the input to a flip-flop before an active clock edge is applied.

Options- A. True

- B. False Discuss

- 4. A method for the automated testing of printed circuit boards is called a(n) ________.

Options- A. bed-of-nails

- B. LUT

- C. CLB

- D. CPLD Discuss

- 5. Which of the following logic families has the shortest propagation delay?

Options- A. CMOS

- B. BiCMOS

- C. ECL

- D. 74SXX Discuss

- 6. What is the input/output pin configuration of the GAL22V10?

Options- A. 10 output pins and 12 input pins

- B. 2 special-purpose pins

- C. 8 pins that are either inputs or outputs

- D. All of the above Discuss

- 7. List the state of each output pin of a 7447 if RBI = 0, LT = 1, A0 = 1, A1 = 0, A2 = 0, and A3 = 1.

Options- A. RBO = 0, a = 0, b = 0, c = 0, d = 1, e = 1, f = 0, g = 0

- B. RBO = 1, a = 0, b = 0, c = 0, d = 1, e = 1, f = 0, g = 0

- C. RBO = 0, a = 0, b = 0, c = 0, d = 0, e = 1, f = 0, g = 0

- D. RBO = 1, a = 0, b = 0, c = 0, d = 0, e = 1, f = 0, g = 0 Discuss

- 8. Which statement below best describes the function of a decoder?

Options- A. A decoder will convert a decimal number into the proper binary equivalent.

- B. A decoder will convert a binary number into a specific output representing a particular character or digit.

- C. Decoders are used to prevent improper operation of digital systems.

- D. Decoders are special ICs that are used to make it possible for one brand of computer to talk to another. Discuss

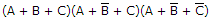

- 9. Convert the following SOP expression to an equivalent POS expression.

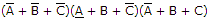

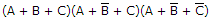

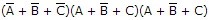

Options- A.

- B.

- C.

- D.

Discuss

Discuss

- 10. What is the difference between the 74HC00 series and the 74HCT00 series of CMOS logic?

Options- A. The HCT series is faster.

- B. The HCT series is slower.

- C. The HCT series is input and output voltage compatible with TTL.

- D. The HCT series is not input and output voltage compatible with TTL. Discuss

More questions

Correct Answer:

Correct Answer: True

Correct Answer: False

Correct Answer: bed-of-nails

Correct Answer: ECL

Correct Answer: 10 output pins and 12 input pins

Correct Answer: RBO = 0, a = 0, b = 0, c = 0, d = 1, e = 1, f = 0, g = 0

Correct Answer: A decoder will convert a binary number into a specific output representing a particular character or digit.

Correct Answer:

Correct Answer: The HCT series is input and output voltage compatible with TTL.

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.