Discussion

Home ‣ Digital Electronics ‣ Flip-Flops See What Others Are Saying!

- Question

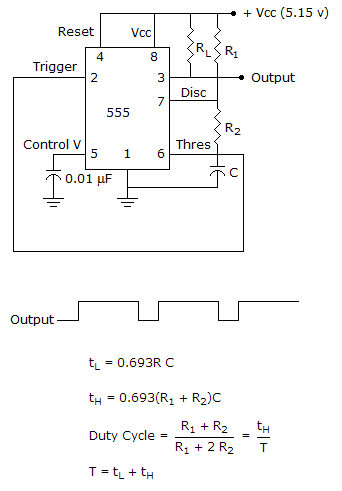

A 555 timer is connected for astable operation as shown below along with the output waveform. It is determined that the duty cycle should be 0.5. What steps need to be taken to correct the duty cycle, while maintaining the same output frequency?

Options- A. Increase the value of C.

- B. Increase Vcc and decrease RL.

- C. Decrease R1 and R2.

- D. Decrease R1 and increase R2.

- Correct Answer

- Decrease R1 and increase R2.

- 1. How is a J-K flip-flop made to toggle?

Options- A. J = 0, K = 0

- B. J = 1, K = 0

- C. J = 0, K = 1

- D. J = 1, K = 1 Discuss

- 2. The following combination is correct for an ODD parity data transmission system:

data = 011011100 and parity = 0

Options- A. True

- B. False Discuss

- 3. A major disadvantage of the mask ROM is that it:

Options- A. is time consuming to change the stored data when system requirements change

- B. is very expensive to change the stored data when system requirements change

- C. cannot be reprogrammed if stored data needs to be changed

- D. has an extremely short life expectancy and requires frequent replacement Discuss

- 4. One disadvantage of the tracking A/D converter is:

Options- A. that it requires two counters?one for up and one for down.

- B. that the binary output will oscillate between two binary states when the analog input is constant.

- C. the need for an accurate clock reference for the counter.

- D. the need for a latch and its associated control circuit. Discuss

- 5. Hexadecimal 44 is ________ in decimal.

Options- A. 6810

- B. 7410

- C. 7710

- D. 9810 Discuss

- 6. The CPU contains all the circuitry for ________.

Options- A. storing data

- B. keeping track of time

- C. fetching and interpreting instructions

- D. Internet operations Discuss

- 7. The Q output of a flip-flop is normally HIGH when the device is in the "CLEAR" or "RESET" state.

Options- A. True

- B. False Discuss

- 8. What must be done to interface TTL to CMOS?

Options- A. A dropping resistor must be used on the CMOS 12 V supply to reduce it to 5 V for the TTL.

- B. As long as the CMOS supply voltage is 5 V, they can be interfaced; however, the fan-out of the TTL is limited to five CMOS gates.

- C. A 5 V Zener diode must be placed across the inputs of the TTL gates in order to protect them from the higher output voltages of the CMOS gates.

- D. A pull-up resistor must be used between the TTL output-CMOS input node and Vcc; the value of RP will depend on the number of CMOS gates connected to the node. Discuss

- 9. The input levels to a flip-flop must be maintained for a minimum time period both before and after the edge of the clock signal is applied.

Options- A. True

- B. False Discuss

- 10. A Celsius thermometer is an application for the 8051 microcontroller.

Options- A. True

- B. False Discuss

More questions

Correct Answer: J = 1, K = 1

Correct Answer: True

Correct Answer: cannot be reprogrammed if stored data needs to be changed

Correct Answer: that the binary output will oscillate between two binary states when the analog input is constant.

Correct Answer: 6810

Correct Answer: fetching and interpreting instructions

Correct Answer: False

Correct Answer: A pull-up resistor must be used between the TTL output-CMOS input node and Vcc; the value of RP will depend on the number of CMOS gates connected to the node.

Correct Answer: True

Correct Answer: True

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.