Discussion

Home ‣ Digital Electronics ‣ Integrated Circuit Technologies See What Others Are Saying!

- Question

A certain gate draws 1.8 µA when its output is HIGH and 3.3 µA when its output is LOW. VCC is 5 V and the gate is operated on a 50% duty cycle. What is the average power dissipation (PD)?

Options- A. 2.55 µW

- B. 1.27 µW

- C. 12.75 µW

- D. 5 µW

- Correct Answer

- 12.75 µW

- 1. VHDL was created as a very flexible language and it allows us to define the operation of clocked devices in the code without relying on logic primitives.

Options- A. True

- B. False Discuss

- 2. A demultiplexer takes a dual input data value and routes it to one of several outputs.

Options- A. True

- B. False Discuss

- 3. The output of a phototransister is determined by the presence or absence of light at its base input.

Options- A. True

- B. False Discuss

- 4. In VHDL, in which declaration section is a COMPONENT declared?

Options- A. Architecture

- B. Library

- C. Entity

- D. Port map Discuss

- 5. Digital circuits cannot perform logic comparisons since the circuit can have only one of two values at any instant.

Options- A. True

- B. False Discuss

- 6. The resolution of a 6-bit DAC is ________.

Options- A. 63%

- B. 64%

- C. 15.9%

- D. 1.59% Discuss

- 7. Convert the binary number 1011010 to hexadecimal.

Options- A. 5B

- B. 5F

- C. 5A

- D. 5C Discuss

- 8. The decimal fraction 1/4 can be written in binary as________.

Options- A. 0.010

- B. 0.100

- C. 0.110

- D. 0.011 Discuss

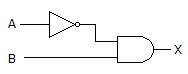

- 9. The gates in this figure are implemented using TTL logic. If the input of the inverter is open, and you apply logic pulses to point B, the output of the AND gate will be ________.

Options- A. a steady LOW

- B. a steady HIGH

- C. an undefined level

- D. pulses Discuss

- 10. Why have PLDs taken over so much of the market?

Options- A. One PLD does the work of many ICs.

- B. The PLDs are cheaper.

- C. Less power is required.

- D. All of the above Discuss

More questions

Correct Answer: True

Correct Answer: False

Correct Answer: True

Correct Answer: Architecture

Correct Answer: False

Correct Answer: 1.59%

Correct Answer: 5A

Correct Answer: 0.010

Correct Answer: a steady LOW

Correct Answer: All of the above

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.