Discussion

Home ‣ Digital Electronics ‣ Interfacing to the Analog World See What Others Are Saying!

- Question

A 4-bit stairstep-ramp A/D converter has a clock frequency of 100 kHz and maximum input voltage of 10 V.

Options- A. The maximum number of samples per second will be 6250.

- B. The maximum sample rate will be 100,000 samples/second.

- C. The minimum sample rate will be 6250 samples/second.

- D. The minimum sample rate will be 100,000 samples/second.

- Correct Answer

- The minimum sample rate will be 6250 samples/second.

- 1. With an OR gate, the output is HIGH only when both inputs are HIGH.

Options- A. True

- B. False Discuss

- 2. Which format requires fewer conductors?

Options- A. Parallel

- B. Serial

- C. Both are the same

- D. Cannot tell Discuss

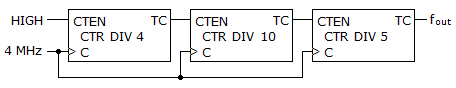

- 3. ________ is the output frequency of the counter shown below.

Options- A. 4 MHz

- B. 20 kHz

- C. 210.5 kHz

- D. 800 Hz Discuss

- 4. A good example of the use of a digital representation of an analog quantity is the audio recording of music.

Options- A. True

- B. False Discuss

- 5. Which of the following RAM timing parameters determine its operating speed?

Options- A. tACC

- B. tAA and tACS

- C. tCO and tOD

- D. tRC and tWC Discuss

- 6. Typically, how often is DRAM refreshed?

Options- A. 2 to 8 ms

- B. 4 to 16 ms

- C. 8 to 16 µs

- D. 1 to 2 µs Discuss

- 7. The architecture of a PAL differs slightly from that of a PROM.

Options- A. True

- B. False Discuss

- 8. CCD stands for ________.

Options- A. capacitor charging device

- B. capacitor-capacitor drain

- C. charged-capacitor device

- D. charge-coupled device Discuss

- 9. Dynamic memories, such as the 2118 16K × 1 RAM, have to multiplex the address bus.

Options- A. True

- B. False Discuss

- 10. The total amount of external code memory that can be interfaced to the 8051 is:

Options- A. 32K

- B. 64K

- C. 128K

- D. 256K Discuss

More questions

Correct Answer: False

Correct Answer: Serial

Correct Answer: 20 kHz

Correct Answer: False

Correct Answer: tRC and tWC

Correct Answer: 4 to 16 ms

Correct Answer: True

Correct Answer: charge-coupled device

Correct Answer: True

Correct Answer: 64K

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.