Discussion

Home ‣ Digital Electronics ‣ Interfacing to the Analog World See What Others Are Saying!

- Question

What is the maximum conversion time for a counter-ramp ADC with 8-bit resolution and a clock frequency of 20 kHz?

Options- A. 12.8 ms

- B. 6.4 ms

- C. 0.05 ms

- D. 0.4 ms

- Correct Answer

- 12.8 ms

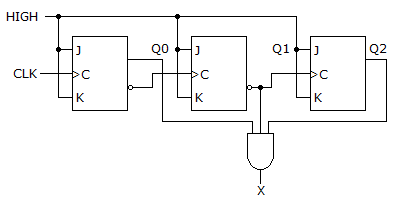

- 1. What decimal value is required to produce an output at "X"?

Options- A. 1

- B. 1 or 4

- C. 2

- D. 5 Discuss

- 2. Which is not a part of a GAL16V8's OLMC?

Options- A. TSMUX

- B. OMUX

- C. FMUX

- D. PSMUX Discuss

- 3. Output will be a LOW for any case when one or more inputs are zero for a(n):

Options- A. OR gate

- B. NOT gate

- C. AND gate

- D. NOR gate Discuss

- 4. The sum of 11101 + 10111 equals ________.

Options- A. 110011

- B. 100001

- C. 110100

- D. 100100 Discuss

- 5. Hex is often used in digital applications as a shorthand way to represent strings of bits.

Options- A. True

- B. False Discuss

- 6. Four cascaded modulus-10 counters have an overall modulus of ________.

Options- A. 10

- B. 100

- C. 1,000

- D. 10,000 Discuss

- 7. VHDL is not a new language.

Options- A. True

- B. False Discuss

- 8. Which is not a removable drive?

Options- A. Zip

- B. Jaz

- C. Hard

- D. SuperDisk Discuss

- 9. Which microprocessor has multiplexed data and address lines?

Options- A. 8086/8088

- B. 80286

- C. 80386

- D. Pentium Discuss

- 10. One of the stages in a register consists of a latch.

Options- A. True

- B. False Discuss

More questions

Correct Answer: 5

Correct Answer: PSMUX

Correct Answer: AND gate

Correct Answer: 110100

Correct Answer: True

Correct Answer: 10,000

Correct Answer: True

Correct Answer: Hard

Correct Answer: 8086/8088

Correct Answer: True

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.