Discussion

Home ‣ Digital Electronics ‣ Digital Arithmetic Operations and Circuits Comments

- Question

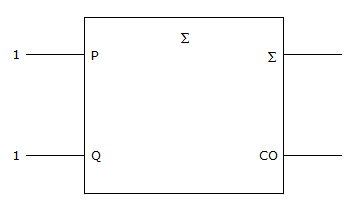

Which of the statements below best describes the given figure?

Options- A. Half-carry adder; Sum = 0, Carry = 1

- B. Half-carry adder; Sum = 1, Carry = 0

- C. Full-carry adder; Sum = 1, Carry = 0

- D. Full-carry adder; Sum = 1, Carry = 1

- Correct Answer

- Half-carry adder; Sum = 0, Carry = 1

- 1. What distinguishes the look-ahead-carry adder?

Options- A. It is slower than the ripple-carry adder.

- B. It is easier to implement logically than a full adder.

- C. It is faster than a ripple-carry adder.

- D. It requires advance knowledge of the final answer. Discuss

- 2. What are constants in VHDL code?

Options- A. Fixed numbers represented by a name

- B. Fixed variables used in functions

- C. Fixed number types

- D. Constants do not exist in VHDL code. Discuss

- 3. Convert each of the signed decimal numbers to an 8-bit signed binary number (two's-complement).

+7 ?3 ?12

Options- A. 0000 0111 1111 1101 1111 0100

- B. 1000 0111 0111 1101 0111 0100

- C. 0000 0111 0000 0011 0000 1100

- D. 0000 0111 1000 0011 1000 1100 Discuss

- 4. Why is a fast-look-ahead carry circuit used in the 7483 4-bit full-adder?

Options- A. to decrease the cost

- B. to make it smaller

- C. to slow down the circuit

- D. to speed up the circuit Discuss

- 5. The carry propagation delay in full-adder circuits:

Options- A. is normally not a consideration because the delays are usually in the nanosecond range.

- B. decreases in a direct ratio to the total number of FA stages.

- C. is cumulative for each stage and limits the speed at which arithmetic operations are performed.

- D. increases in a direct ratio to the total number of FA stages but is not a factor in limiting the speed of arithmetic operations. Discuss

- 6. How many BCD adders would be required to add the numbers 97310 + 3910?

Options- A. 3

- B. 4

- C. 5

- D. 6 Discuss

- 7. An input to the mode pin of an arithmetic/logic unit (ALU) determines if the function will be:

Options- A. one's-complemented

- B. arithmetic or logic

- C. positive or negative

- D. with or without carry Discuss

- 8. The binary adder circuit is designed to add ________ binary numbers at the same time.

Options- A. 2

- B. 4

- C. 6

- D. 8 Discuss

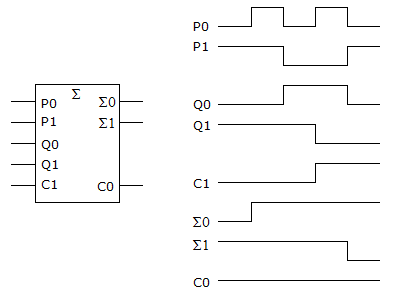

- 9. What is wrong, if anything, with the circuit in the given figure based on the logic analyzer display accompanying the circuit?

Options- A. The CO terminal is shorted to ground.

- B. The S1 output is shorted to Vcc.

- C. The P1 input is not being added into the total.

- D. Nothing is wrong; the circuit is functioning correctly. Discuss

- 10. Half-adders can be combined to form a full-adder with no additional gates.

Options- A. True

- B. False Discuss

Digital Arithmetic Operations and Circuits problems

Search Results

Correct Answer: It is faster than a ripple-carry adder.

Correct Answer: Fixed numbers represented by a name

Correct Answer: 0000 0111 1111 1101 1111 0100

Correct Answer: to speed up the circuit

Correct Answer: is cumulative for each stage and limits the speed at which arithmetic operations are performed.

Correct Answer: 3

Correct Answer: arithmetic or logic

Correct Answer: 2

Correct Answer: The P1 input is not being added into the total.

Correct Answer: False

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.