Discussion

Home ‣ Digital Electronics ‣ Digital Arithmetic Operations and Circuits Comments

- Question

Find the 2's complement of ?1101102.

Options- A. 1101002

- B. 1010102

- C. 0010012

- D. 0010102

- Correct Answer

- 0010102

- 1. The 2's-complement system is to be used to add the signed binary numbers 11110010 and 11110011. Determine, in decimal, the sign and value of each number and their sum.

Options- A. ?113 and ?114, ?227

- B. ?14 and ?13, ?27

- C. ?11 and ?16, ?27

- D. ?27 and ?13, ?40 Discuss

- 2. Subtract the following binary numbers.

0101 1000 1010 0011 1101 1110 ?0010 0011 ?0011 1000 ?0101 0111

Options- A. 0011 0100 0110 1010 1000 0110

- B. 0011 0101 0110 1011 1000 0111

- C. 0011 0101 0110 1010 1000 0111

- D. 0011 0101 0110 1010 1000 0110 Discuss

- 3. Convert each of the following signed binary numbers (two's-complement) to a signed decimal number.

00000101 11111100 11111000

Options- A. ?5 +4 +8

- B. +5 ?4 ?8

- C. ?5 +252 +248

- D. +5 ?252 ?248 Discuss

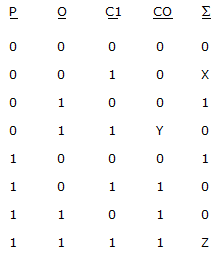

- 4. The truth table for a full adder is shown below. What are the values of X, Y, and Z?

Options- A. X = 0, Y = 1, Z = 1

- B. X = 1, Y = 1, Z = 1

- C. X = 1, Y = 0, Z = 1

- D. X = 0, Y = 0, Z = 1 Discuss

- 5. Solve this BCD problem: 0100 + 0110 =

Options- A. 00010000BCD

- B. 00010111BCD

- C. 00001011BCD

- D. 00010011BCD Discuss

- 6. The carry propagation delay in full-adder circuits:

Options- A. is normally not a consideration because the delays are usually in the nanosecond range.

- B. decreases in a direct ratio to the total number of FA stages.

- C. is cumulative for each stage and limits the speed at which arithmetic operations are performed.

- D. increases in a direct ratio to the total number of FA stages but is not a factor in limiting the speed of arithmetic operations. Discuss

- 7. Why is a fast-look-ahead carry circuit used in the 7483 4-bit full-adder?

Options- A. to decrease the cost

- B. to make it smaller

- C. to slow down the circuit

- D. to speed up the circuit Discuss

- 8. Convert each of the signed decimal numbers to an 8-bit signed binary number (two's-complement).

+7 ?3 ?12

Options- A. 0000 0111 1111 1101 1111 0100

- B. 1000 0111 0111 1101 0111 0100

- C. 0000 0111 0000 0011 0000 1100

- D. 0000 0111 1000 0011 1000 1100 Discuss

- 9. What are constants in VHDL code?

Options- A. Fixed numbers represented by a name

- B. Fixed variables used in functions

- C. Fixed number types

- D. Constants do not exist in VHDL code. Discuss

- 10. What distinguishes the look-ahead-carry adder?

Options- A. It is slower than the ripple-carry adder.

- B. It is easier to implement logically than a full adder.

- C. It is faster than a ripple-carry adder.

- D. It requires advance knowledge of the final answer. Discuss

Digital Arithmetic Operations and Circuits problems

Search Results

Correct Answer: ?14 and ?13, ?27

Correct Answer: 0011 0101 0110 1011 1000 0111

Correct Answer: +5 ?4 ?8

Correct Answer: X = 1, Y = 1, Z = 1

Correct Answer: 00010000BCD

Correct Answer: is cumulative for each stage and limits the speed at which arithmetic operations are performed.

Correct Answer: to speed up the circuit

Correct Answer: 0000 0111 1111 1101 1111 0100

Correct Answer: Fixed numbers represented by a name

Correct Answer: It is faster than a ripple-carry adder.

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.