Discussion

Home ‣ Digital Electronics ‣ Combinational Logic Analysis Comments

- Question

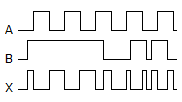

The following waveform pattern is for a(n) ________.

Options- A. 2-input AND gate

- B. 2-input OR gate

- C. Exclusive-OR gate

- D. None of the above

- Correct Answer

- Exclusive-OR gate

- 1. One positive pulse with tw = 75 µs is applied to one of the inputs of an exclusive-OR circuit. A second positive pulse with tw = 15 µs is applied to the other input beginning 20 µs after the leading edge of the first pulse. Which statement describes the output in relation to the inputs?

Options- A. The exclusive-OR output is a 20 µs pulse followed by a 40 µs pulse, with a separation of 15 µs between the pulses.

- B. The exclusive-OR output is a 20 µs pulse followed by a 15 µs pulse, with a separation of 40 µs between the pulses.

- C. The exclusive-OR output is a 15 µs pulse followed by a 40 µs pulse.

- D. *The exclusive-OR output is a 20 µs pulse followed by a 15 µs pulse, followed by a 40 µs pulse. Discuss

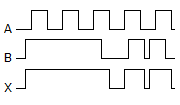

- 2. The following waveform pattern is for a(n) ________.

Options- A. 2-input AND gate

- B. 2-input OR gate

- C. Exclusive-OR gate

- D. None of the above Discuss

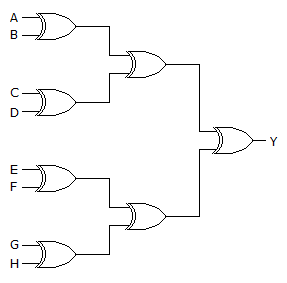

- 3. The 8-input XOR circuit shown has an output of Y = 1. Which input combination below (ordered A ? H) is correct?

Options- A. 10111100

- B. 10111000

- C. 11100111

- D. 00011101 Discuss

- 4. The inverter can be produced with how many NAND gates?

Options- A. 1

- B. 2

- C. 3

- D. 4 Discuss

- 5. The output of an exclusive-NOR gate is 1. Which input combination is correct?

Options- A. A = 1, B = 0

- B. A = 0, B = 1

- C. A = 0, B = 0

- D. none of the above Discuss

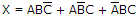

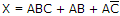

- 6. How many AND gates are required to implement the Boolean expression,

?

?

Options- A. 1

- B. 2

- C. 3

- D. 4 Discuss

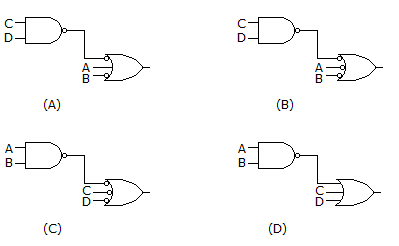

- 7. Implementing the expression

using NAND logic, we get:

using NAND logic, we get:

Options- A. (A)

- B. (B)

- C. (C)

- D. (D) Discuss

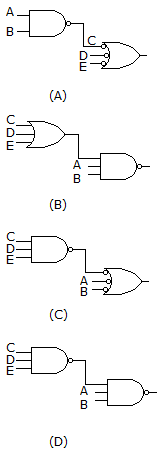

- 8. Implementing the expression

using NAND logic, we get:

using NAND logic, we get:

Options- A. (A)

- B. (B)

- C. (C)

- D. (D) Discuss

- 9. Implementation of the Boolean expression

results in ________.

results in ________.

Options- A. three AND gates, one OR gate

- B. three AND gates, one NOT gate, one OR gate

- C. three AND gates, one NOT gate, three OR gates

- D. three AND gates, three OR gates Discuss

- 10. How many NOT gates are required to implement the Boolean expression,

?

?

Options- A. 1

- B. 2

- C. 4

- D. 5 Discuss

Combinational Logic Analysis problems

Search Results

Correct Answer: *The exclusive-OR output is a 20 µs pulse followed by a 15 µs pulse, followed by a 40 µs pulse.

Correct Answer: 2-input OR gate

Correct Answer: 10111100

Correct Answer: 1

Correct Answer: A = 0, B = 0

Correct Answer: 3

Correct Answer: (B)

Correct Answer: (D)

Correct Answer: three AND gates, one NOT gate, one OR gate

Correct Answer: 2

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.