Discussion

Home ‣ Digital Electronics ‣ Flip-Flops Comments

- Question

How can the cross-coupled NAND flip-flop be made to have active-HIGH S-R inputs?

Options- A. It can't be done.

- B. Invert the Q outputs.

- C. Invert the S-R inputs.

- Correct Answer

- Invert the S-R inputs.

- 1. A J-K flip-flop is in a "no change" condition when ________.

Options- A. J = 1, K = 1

- B. J = 1, K = 0

- C. J = 0, K = 1

- D. J = 0, K = 0 Discuss

- 2. Latches constructed with NOR and NAND gates tend to remain in the latched condition due to which configuration feature?

Options- A. cross coupling

- B. gate impedance

- C. low input voltages

- D. asynchronous operation Discuss

- 3. The output pulse width for a 555 monostable circuit with R1 = 3.3 kΩ and C1 = 0.02 µF is ________.

Options- A. 7.3 µs

- B. 73 µs

- C. 7.3 ms

- D. 73 ms Discuss

- 4. With four J-K flip-flops wired as an asynchronous counter, the first output change of divider #4 indicates a count of how many input clock pulses?

Options- A. 16

- B. 8

- C. 4

- D. 2 Discuss

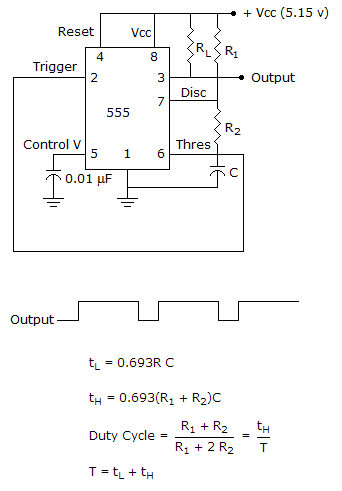

- 5. A 555 timer is connected for astable operation as shown below along with the output waveform. It is determined that the duty cycle should be 0.5. What steps need to be taken to correct the duty cycle, while maintaining the same output frequency?

Options- A. Increase the value of C.

- B. Increase Vcc and decrease RL.

- C. Decrease R1 and R2.

- D. Decrease R1 and increase R2. Discuss

- 6. On a master-slave flip-flop, when is the master enabled?

Options- A. when the gate is LOW

- B. when the gate is HIGH

- C. both of the above

- D. neither of the above Discuss

- 7. Why are the S and R inputs of a gated flip-flop said to be synchronous?

Options- A. They must occur with the gate.

- B. They occur independent of the gate. Discuss

- 8. The circuit given below fails to function; the inputs are checked with a logic probe and the following indications are obtained: CLK, J1, J2, J3, K1, K2, and K3 are pulsing. Q and

are HIGH.

are HIGH.  and PRE are LOW. What could be causing the problem?

and PRE are LOW. What could be causing the problem?

Options- A. There is no problem.

- B. The clock should be held HIGH.

- C. The PRE is stuck LOW.

- D. The CLR is stuck HIGH. Discuss

- 9. An RC circuit used in a 74122 retriggerable one-shot has an REXT of 100 kΩ and a CEXT of 0.005 µF. The pulse width is ________.

Options- A. 70 µs

- B. 16 µs

- C. 160 µs

- D. 32 µs Discuss

- 10. In VHDL, how is each instance of a component addressed?

Options- A. A name followed by a colon and the name of the library primitive

- B. A name followed by a semicolon and the component type

- C. A name followed by the library being used

- D. A name followed by the component library number Discuss

Flip-Flops problems

Search Results

Correct Answer: J = 0, K = 0

Correct Answer: cross coupling

Correct Answer: 73 µs

Correct Answer: 8

Correct Answer: Decrease R1 and increase R2.

Correct Answer: when the gate is HIGH

Correct Answer: They must occur with the gate.

Correct Answer: The PRE is stuck LOW.

Correct Answer: 160 µs

Correct Answer: A name followed by a colon and the name of the library primitive

Comments

There are no comments.More in Digital Electronics:

Programming

Copyright ©CuriousTab. All rights reserved.